# CDCL3000C0-0002R7STB

# **ULTRACAPACITOR CELL**

#### **SERIES**

#### **CDCL ULTRACAPACITOR CELL**

| Rev     | Date     | Revision of historical records |

|---------|----------|--------------------------------|

| V2019-1 | 24-10-19 | The First Release              |

| V2020-1 | 14-5-20  | Version Update                 |

#### **SCOPE**

These are the specifications of SPSCAP (Electric Double Layer Capacitor) which you are using, please review this document and approve it.

## **FEATURES**

Low ESR & High Power Density

Over 1,000,000 duty cycles

Threaded connection

## **APPLICATIONS**

**EV/HEV**

Hybrid driven trains

Mass transportation braking energy recovery system

Heavy duty machinery

Locomotive engine start system

Document number: DT14-08-201904-E Rev. & Date: V2020-1 2020.05.14

2.7V 3000F CDCL-STB

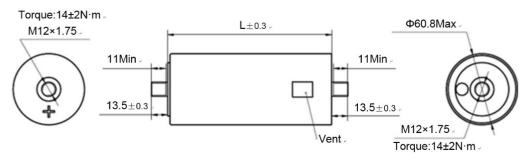

## **CONSTRUCTION AND DIMENSIONS**

#### 1) Construction

Inside structure: fold anode and cathode electrode with separator

Outer structure: aluminum case, insulating sleeve

#### 2) Dimensions

| DADT MUMBED          | DIMENSION(mm) |  |

|----------------------|---------------|--|

| PART NUMBER          | L             |  |

| CDCL2000C0-0002R7STB | 138.0         |  |

| PART NUMBER NAMING SYSTEM |                          |       |                     |      |                   |       |        |                    |  |

|---------------------------|--------------------------|-------|---------------------|------|-------------------|-------|--------|--------------------|--|

|                           | CDCL                     | 3000  | 3000 C 0            |      | 0002              | R     | 7      | STB                |  |

| Pro                       | oduct Series             | Nomir | nal Capacitance (F) |      | Rated Voltage (V) |       | V) Ter | Terminal Design    |  |

| С                         | Cell                     | 3000  | 3000                |      | 0002              | 2     | CT.    | Threaded           |  |

| D                         | Electric<br>double layer | С     | Decimal             | Dash | R                 | Decim | ST     | connection         |  |

| С                         | Cylindrical              | 0     | 0.0                 |      | 7                 | 0.7   | В      | Improved<br>Design |  |

| L                         | Large                    | U     | 0.0                 |      |                   |       | В      |                    |  |

Document number: DT14-08-201904-E 2.7V 3000F CDCL-STB Rev. & Date: V2020-1 2020.05.14

| GENERAL CHARACTERISTICS                                      |                  |

|--------------------------------------------------------------|------------------|

| Items                                                        | Specification    |

| Rated Voltage (V DC)                                         | 2.7              |

| Surge Voltage (V DC)                                         | 2.85             |

| Operating Temp. (°C)                                         | -40 <b>∼</b> +65 |

| Rated Capacitance (F)                                        | 3000             |

| Capacitance Tolerance                                        | 0% ~ 20%         |

| ESR Max. (AC@1KHz, mΩ)                                       | 0.22             |

| ESR Max. (DC, $m\Omega$ )                                    | 0.29             |

| Maximum Continuous Current (ΔT=15°C, A)                      | 129              |

| Maximum Continuous Current (ΔT=40°C, A)                      | 211              |

| Maximum Peak Current (A) (1s)                                | 2166             |

| Max.LC (Room Temp. after 72hrs, mA)                          | 5.2              |

| Typical Thermal Resistance (R <sub>th</sub> , Housing, °C/W) | 3.1              |

| Typical Thermal Capacitance (C <sub>th</sub> , J/°C)         | 645              |

| Weight (g)                                                   | 548              |

| Energy Stored (Wh)                                           | 3.04             |

## **RELIABILITY SPECIFICATIONS**

| ITEM                     |             | SPECIFICATION                       |                                   | CONDITION                                                 |  |

|--------------------------|-------------|-------------------------------------|-----------------------------------|-----------------------------------------------------------|--|

| Temp.<br>Characteristics | Capacitance | Ctor 1                              | Change within 5% of Initial Value |                                                           |  |

|                          | ESR         | Step. 1                             | Change within 50% of rated value  | Step 1:+25±2°C, 1h<br>Step 2:+65±2°C, 1h                  |  |

|                          | Capacitance | <b>C</b> 1 0                        | Change within 5% of Initial Value |                                                           |  |

|                          | ESR         | Step. 2                             | Change within 50% of rated value  |                                                           |  |

|                          | Capacitance | <b>C</b> 1 0                        | Change within 5% of Initial Value | Step 3: −25±2°C, 1h                                       |  |

|                          | ESR         | Step. 3                             | Change within 50% of rated value  | Step 4: -40±2°C, 1h                                       |  |

|                          | Capacitance |                                     | Change within 5% of Initial Value |                                                           |  |

|                          | ESR         | Step. 4                             | Change within 50% of rated value  |                                                           |  |

| Vibration<br>Test        | Capacitance | Initial Value                       |                                   |                                                           |  |

|                          | ESR         | Initial Value                       |                                   | ISO16750-3 Table 14                                       |  |

|                          | Appearance  | Not Mark                            | ked Defect                        |                                                           |  |

| Thermal<br>Cycle         | Capacitance | Initial Value                       |                                   | Temp.: $-40^{\circ}$ C $\sim 65^{\circ}$ C Cycle times: 6 |  |

|                          | ESR         | Initial Va                          | lue                               | Test Time(One Cycle): -40°C 2hrs,                         |  |

|                          | Appearance  | Not Marked Defect                   |                                   | +65°C 2hrs,<br>Temp change 2hrs                           |  |

|                          | Capacitance | Change within 20% of Initial Value  |                                   | Temp.: +40±2℃                                             |  |

| Humidity Test            | ESR         | Change w                            | vithin 100% of Initial Value      | Humidity: 90-95%RH<br>Test Time: 240±8hrs                 |  |

|                          | Appearance  | Not Marked Defect                   |                                   | lest Time: 240±8nrs                                       |  |

|                          | Capacitance | Change within 20% of Initial Value  |                                   | Temp.: +65±2℃                                             |  |

| DC Life                  | ESR         | Change within 100% of Initial Value |                                   | Voltage: 2.7V                                             |  |

|                          | Appearance  | Not Marked Defect                   |                                   | Time: 1,500hrs                                            |  |

| Shelf Life               | Capacitance | Change within 20% of Initial Value  |                                   | Temp.: +70±2°C<br>Time: 1,000hrs                          |  |

|                          | ESR         | Change within 100% of Initial Value |                                   |                                                           |  |

|                          | Appearance  | Not Mark                            | ked Defect                        |                                                           |  |

| Cycle Life               | Capacitance | Change w                            | vithin 20% of Initial Value       | Taman 25 . 2°C                                            |  |

|                          | ESR         | Change w                            | vithin 100% of Initial Value      | Temp.: +25±2°C<br>Cycles times:<br>1,000,000              |  |

|                          | Appearance  | Not Mark                            | ked Defect                        |                                                           |  |

#### **MEASURING METHOD**

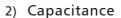

- 1) Charge and Discharge procedure (Figure 1)

- A) Charge the capacitor using constant current I to rated voltage V<sub>0</sub>

- B) Keep rated voltage 5 mins

- C) Discharge the capacitor using constant current I to half rated voltage, record discharge time T<sub>1</sub> during voltage change from V<sub>1</sub>to V<sub>2</sub>

- D) Rest 2-5s, record voltage change △V

- E) Discharge it to a very low voltage around 0.01V

- F)  $V_1 = 85\% V_0 V_2 = 50\% V_0$

$$C = I \cdot T1/(V_1 - V_2)$$

C: Capacitance (F)

I: Constant Discharge Current (A)

Time (S)

V<sub>1</sub>-V<sub>2</sub>: Voltage Change (V)

DC ESR=

$$\Delta V/I$$

DC ESR: DC Equivalent Series Resistance ( $\Omega$ )

ΔV: Voltage Change (V)

I: Constant Discharge Current (A)

Measure AC ESR using LCR meter

Frequency: 1KHz

Voltage: fully discharge

Figure 1

REMARK: SPSCAP EDLC SHOULD BE DISCHARGED WITH RESISTOR FOR AT LEAST 12 HOURS BEFORE MEASUREMENT OF CAPACITANCE OR ESR.

#### **NOTES AND CAUTION**

Please notice below points when you start use SPSCAP.

- 1) The SPSCAP gets polarity through aging/testing process before it is packed, so please mount it in accordance with its polarity to maintain the best condition;

- 2) Please only apply SPSCAP at rated voltage. If you apply more than rated voltage, capacitor will be damaged or broken due to electrolyte inside will be electrolyzed;

- 3) Ambient temperature greatly affects the lifetime of the capacitor, by reducing the temperature by 10°C, lifetime can be approximately doubled;

- 4) Storage: In long term storage, please store SPSCAP in following condition:

- Temp.: 15 ~ 35°C

- Humidity: 40 ~ 75 %RH

- No-dust, non-acidic and/or non-alkaline atmosphere

- Avoid direct sun light

- 5) Do not disassemble SPSCAP. It contains electrolyte;

- 6) Avoid serious mechanical impacts onto capacitor, such as force or twist capacitor;

- 7) Please contact us if you want to subject SPSCAP to severe vibrating conditions exceeding rated specification;

- 8) Please contact us if you want to connect a certain number of single capacitor to make a module;

- 9) Over-rated voltage may be applied to a single SPSCAP in series connection due to the deviation of capacitance and ESR of each SPSCAP. Please inform us if you are using SPSCAP in series connection and please design so as not to apply over-rated voltage to each capacitor, and use SPSCAP from same date code/lot.

All rights reserved. Design and specifications are subjected to change without notice.

#### NINGBO CRRC NEW ENERGY TECHNOLOGY CO.,LTD.

Add: No.199 Shidai Road, Wuxiang Town, Yinzhou District,

Ningbo,Zhejiang,China

Email: info@spscap.com Website: www.spscap.com